## **Outline**

- Motivation

- The Acquisition System Setup

- The Physical Configuration of the Sampling System

- The Sampled Data

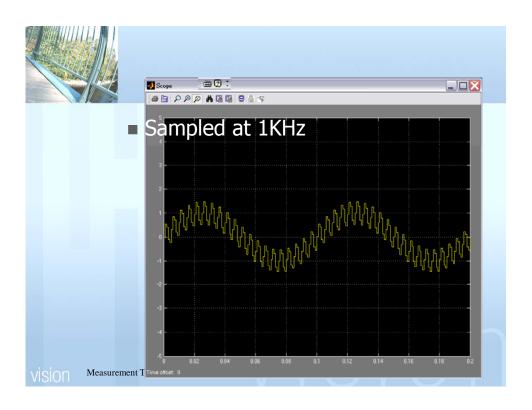

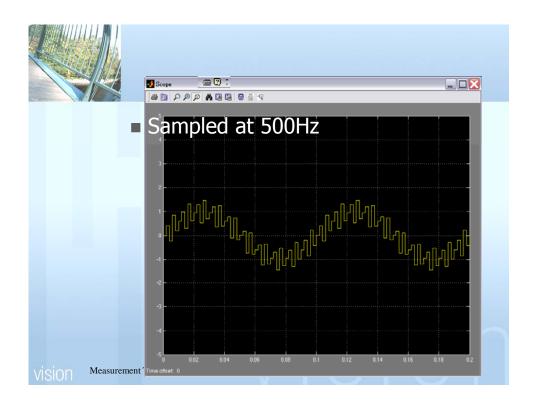

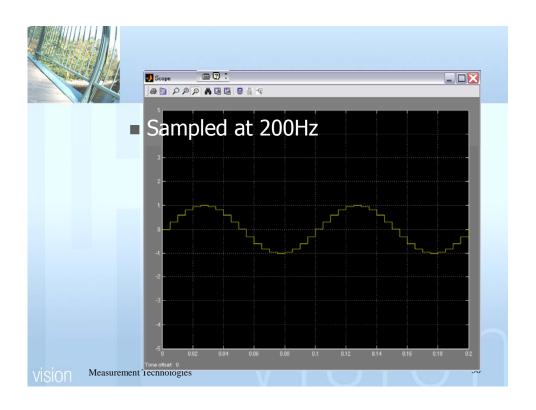

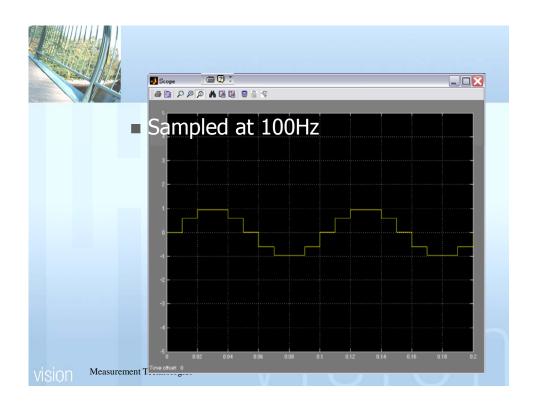

- The Appearance of the Sampled Data

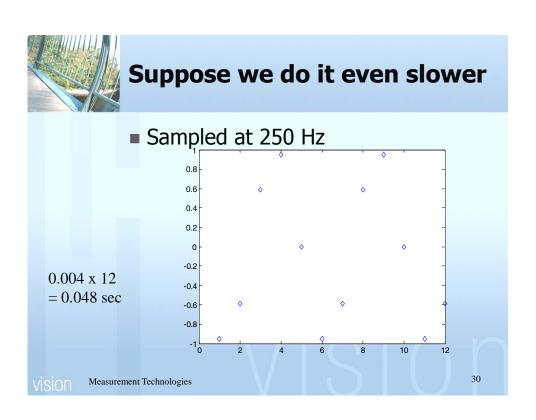

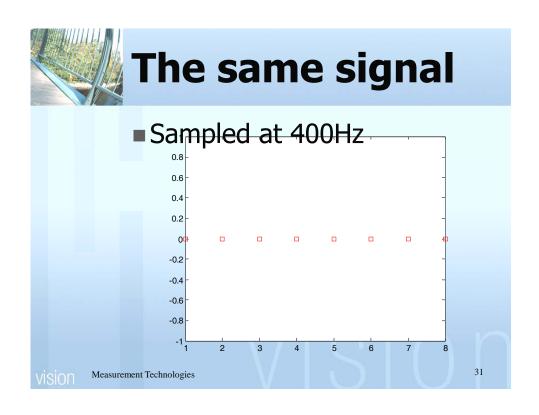

- Sampling Consideration

- Aliasing

- Nyquist Sampling Theorem

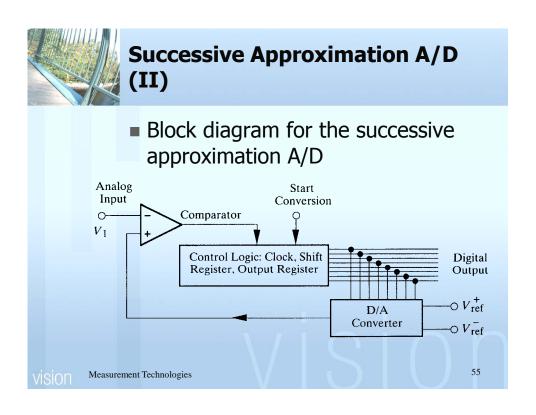

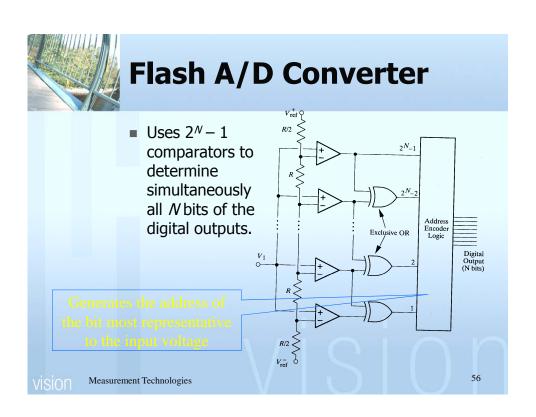

- Various forms of A/D Hardware

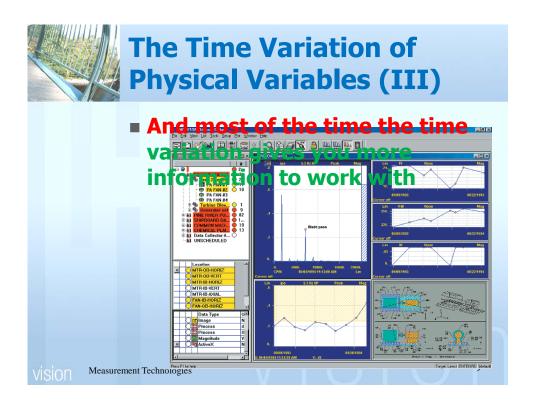

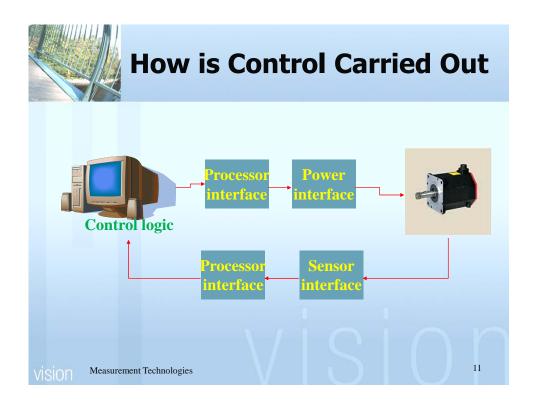

# **How Is A Signal Recorded**

- Computer only works with electrical signals

- A sensor interface converts the signal into a easily handled voltage change

- Computer only works one instruction a time

- A computer interface to measure the magnitude of the voltage at some discrete instances

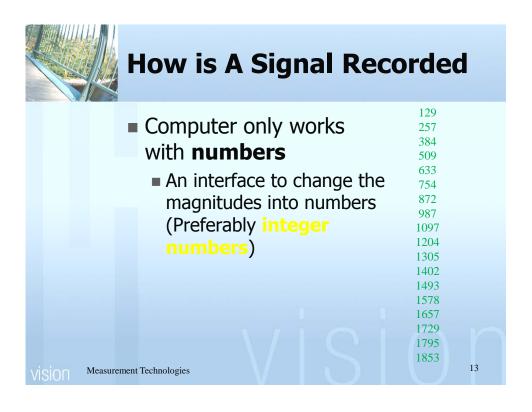

- Computer only works with numbers

VISIO

Measurement Technologies

# **Shannon Sampling Theorem**

Reprinted with corrections from The Bell System Technical Journal, Vol. 27, pp. 379-423, 623-656, July, October, 1948.

A Mathematical Theory of Communication

By C. E. SHANNON

INTRODUCTION

THE recent development of various methods of modulation such as PCM and PPM which exchange bandwidth for signal-to-noise ratio has intensified the interest in a general theory of communication. A busis for such a theory is contained in the important papers of 'Nyquist' and Hartley<sup>2</sup> on this subject. In the present paper we will extend the theory to include a number of new factors, in particular the effect of noise in the channel, and the savings possible due to the statistical structure of the original message and due to the nature of the final destination of the information.

The fundamental problem of communication is that of reproducing at one point either exactly or approximately a message selected at another point. Frequently the messages have meaning, that is they refer to or are correlated according to some system with certain physical or conceptual entities. These semantic aspects of communication are urrelevant to the engineering problem. The significant aspect is that the actual message is one selected from a set of possible messages. The system must be designed to operate for each possible selection, not just the one which will actually be chosen since this is unknown at the time of design. If the number of messages in the set is finite then this number or one monotonic function of this number can be regarded as a measure of the information produced when one message is chosen from the set, all choices being equally likely. As was pointed out by Hartley the most natural choice is the logarithmic function. Although this definition must be generalized considerably when we consider the influence of the statistics of the message and when we have a continuous range of messages, we will in all cases use an essentially logarithmic measure.

The logarithmic measure is more convenient for various reasons:

Measurement reciniologies

## **Shannon Sampling Theorem**

- The Nyquist-Shannon sampling theorem, also known as Whittaker-**Shannon sampling theorem**, is a fundamental result in the field of information theory, in particular telecommunications.

- In addition to E. T. Whittaker (statistical theorem published 1915), Claude Shannon and Harry Nyquist, it is also attributed to Kotelnikov, and sometimes referred to as, simply, the *sampling theorem*.

Measurement Technologies

#### **Claude Elwood Shannon**

(April 30, 1916 – February 24, 2001), an American electrical engineer and mathematician, has been called "the father of information theory", and was the founder of practical digital circuit design theory.

http://www.wikipedia.org

21

■ Edmund Taylor Whittaker (24

October 1873 - 24 March 1956) was an English mathematician, who contributed widely to applied mathematics, mathematical physics and the theory of special functions. He had a particular interest in numerical analysis, but also worked on celestial mechanics and the history of applied mathematics and the history of physics. He was born in Southport, in Merseyside.

http://www.lms.ac.uk/newsletter/328/328\_09.html

ISION <sup>Me</sup>

Measurement Technologies

**Harry Nyquist** (February 7, 1889 – April 4, 1976) was an important contributor to <u>information theory</u>.

He was born in Nilsby, Sweden. He emigrated to the USA in 1907 and entered the University of North Dakota in 1912. He received a Ph.D. in physics at Yale University in 1917. He worked at AT&T from 1917 to 1934, then moved to Bell Telephone Laboratories.

- As an engineer at Bell Laboratories, he did important work on thermal noise ("Johnson-Nyquist noise") and the stability of <u>feedback</u> <u>amplifiers</u>.

- His early theoretical work on determining the bandwidth requirements for transmitting information, as published in "Certain factors affecting telegraph speed" (*Bell System Technical Journal*, 3, 324–346, 1924), laid the foundations for later advances by Claude Shannon, which led to the development of information theory.

- In 1927 Nyquist determined that an analog signal should be sampled at regular intervals over time and at twice the frequency of the signal's bandwidth in order to be converted into an adequate representation of the signal in digital form. Nyquist published his results in the paper *Certain topics in Telegraph Transmission Theory* (1928). This rule is now known as the Nyquist—Shannon sampling

- He retired from Bell Labs in 1954. Nyquist died in Harlingen, Texas on April 4, 1976.

Measurement Technologies

Ref: en.wikipedia.org/wiki/Harry\_Nyquist

23

#### Certain Topics in Telegraph Transmission Theory

H. NYQUIST, MEMBER, A. I. E. E.

- red or the Winner Convention of the A. I. E. E., 13-17, 1928. Reprinted from Transactions of the mary 13-17, 1928. Reprinted from Pransactions of the 644, Feb. 1928. ssed, was with the American Telephone and Telegraph

PROCEEDINGS OF THE SEES, VOL. 90, NO. 2, FEBRUARY 2002

Measurement Technologies

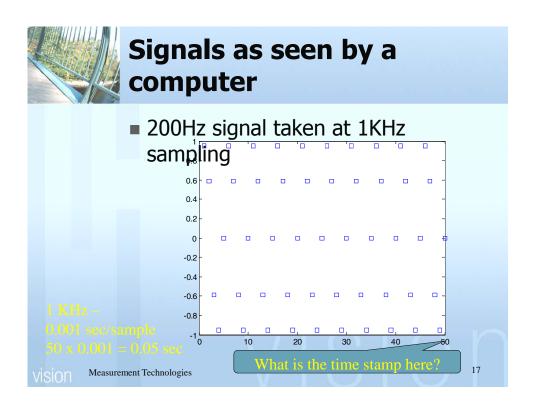

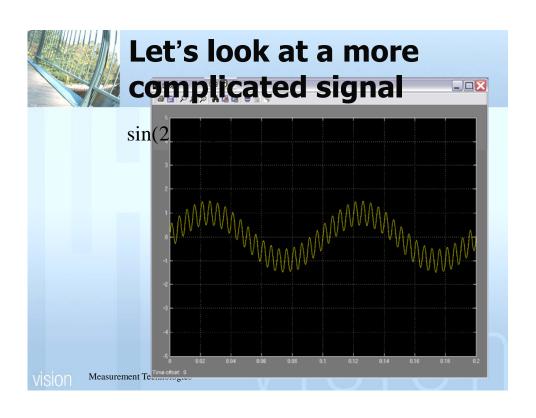

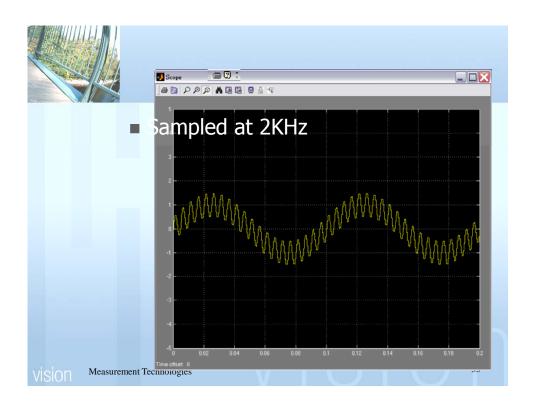

## **Shannon Sampling Theorem**

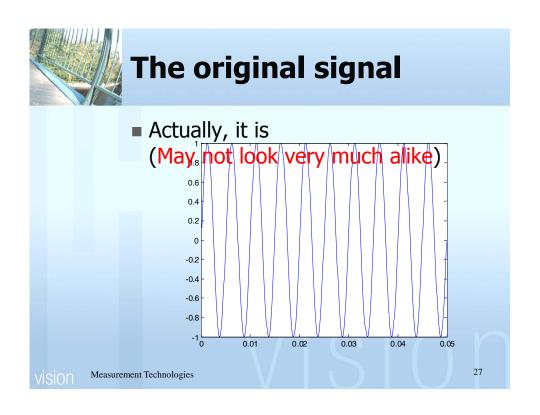

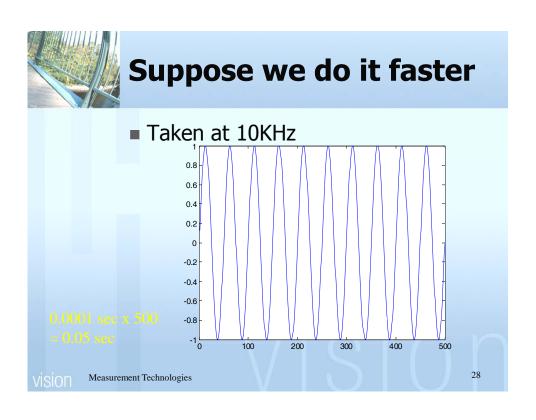

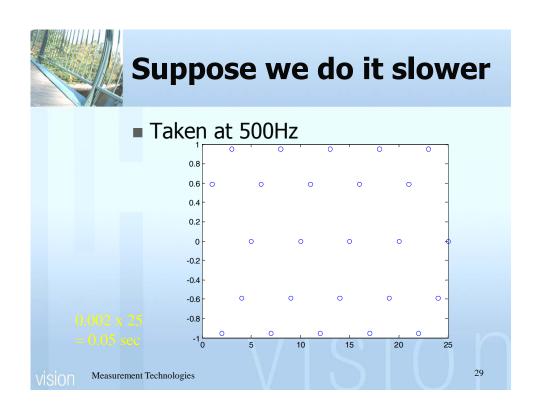

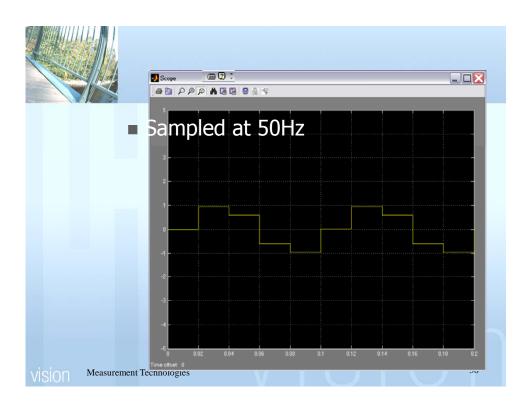

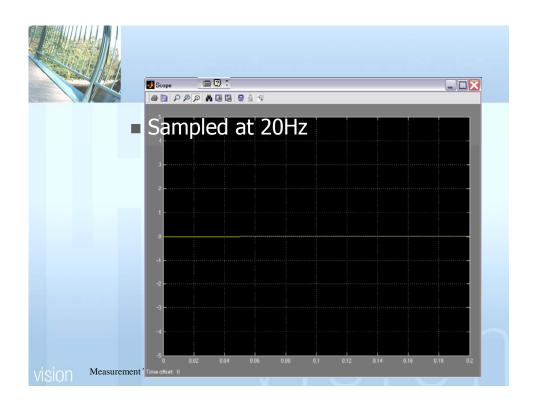

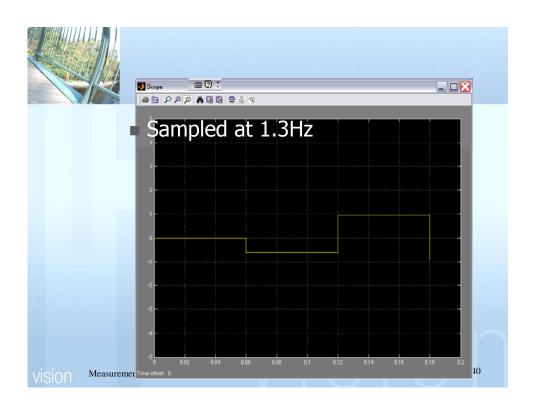

- A signal that is bandlimited is constrained in terms of how fast it can change and therefore how much detail it can convey in between discrete moments of time.

- The sampling theorem means that the discrete samples are a complete representation of the signal if the bandwidth is less than half the sampling rate, which is referred to as the Nyquist frequency.

- Frequency components that are above the Nyquist frequency are subject to a phenomenon called <u>aliasing</u>, which is undesirable in most applications. The severity of the problem depends on the relative strength of the aliased components.

Measurement Technologies

25

### **Shannon Sampling** Theorem

Let *x*(*t*) represent a <u>real-valued continuous-time</u> signal and let *X*(*f*) represent its unitary <u>Fourier transform</u> (to the domain of ordinary frequency, <u>Hz</u>). I.e.:

$X(f) = \Im\{x(t)\} = \int x(t)e^{-j2\pi ft}dt$

The right figure depicts a bandlimited X(f) whose highest frequency is  $f_H$ . i.e.:

X(f) = 0 for  $|f| > f_H$

Then the condition for alias-free sampling at rate  $f_s$  (in samples per

$f_s > 2f_H$  (Nyquist rate)

or equivalently:

$f_H < f_s/2$  (Nyquist frequency)

Spectrum of a bandlimited signal as a function of frequency

X(f)

The time interval between successive samples is a constant, referred to as *sampling interval*. It is given, in seconds, by:  $T = 1/f_s$

And the samples of x(t) are denoted by:  $x(n/f_s) = x(nT), n \in Z$

Measurement Technologies

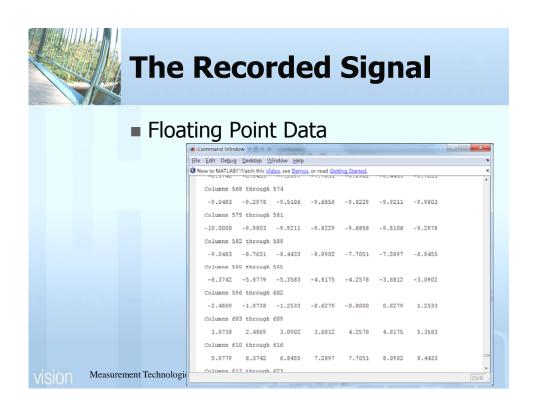

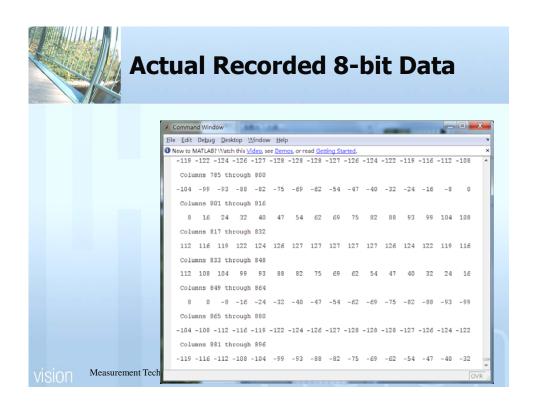

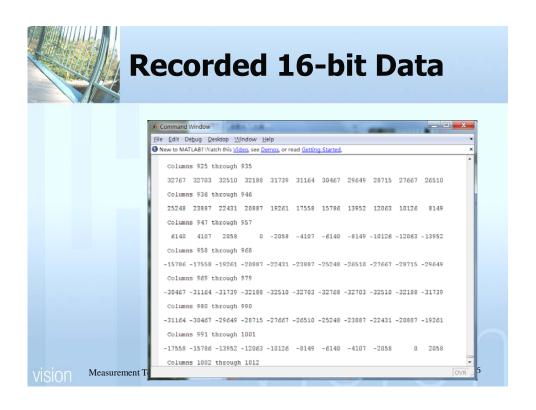

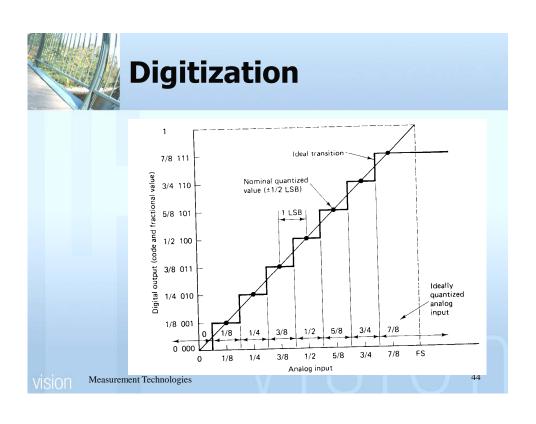

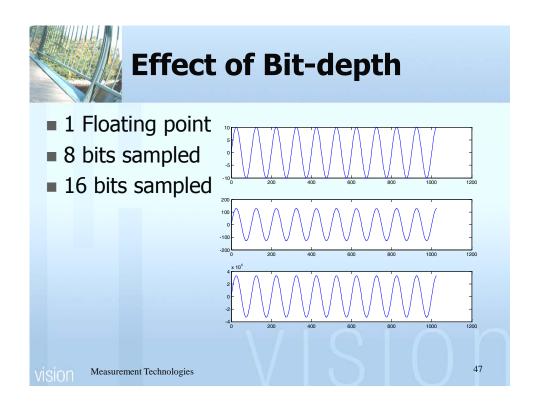

- Consider N-bit A/D converter

- The sampled data

$$n = \left[\frac{V - V_{ref}^{-}}{\Delta V} + \frac{1}{2}\right]_{round}, \quad \Delta V = \frac{V_{ref}^{+} - V_{ref}^{-}}{2^{N} - 1}$$

visior

Measurement Technologies

45

# **In Other Word**

- When sampling data

- 1. Amplify the signal to  $V_{ref}^+ \leftrightarrow V_{ref}^-$  before attaching to A/D

- 2. When recording multiply data by (in\_data\_array)\*△V

to obtain the correct magnitude

VISIO

Measurement Technologies

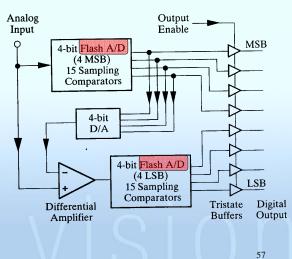

#### Subranging Flash A/D Converter

- Flash converter is too costly

- More practical solution

- Hybrid between the successiveapproximation and the flash converter

Measurement Technologies

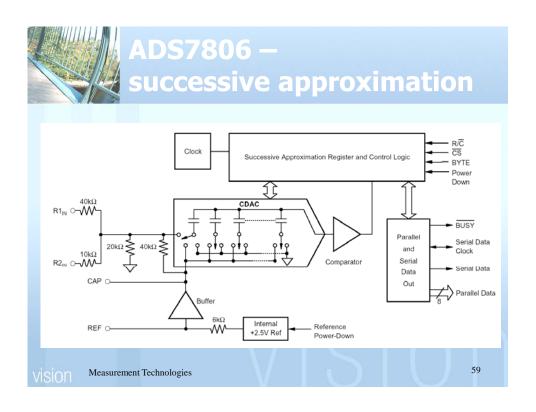

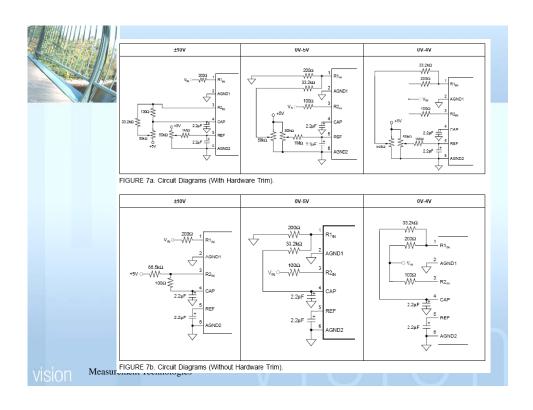

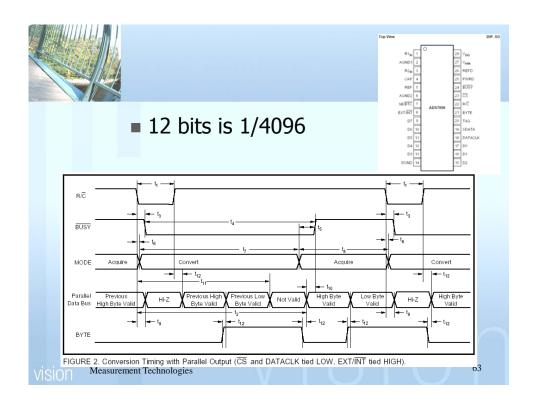

#### **TI ADS7806**

Ref: www.ti.com

- The ADS7806 is a **low-power**, **12-bit**, **sampling Analog-to-Digital (A/D) converter** using state of the art CMOS structures.

- It contains a complete 12-bit, capacitor-based, **Successive Approximation Register (SAR)** A/D converter with sample and-hold, clock, reference, and a microprocessor interface with parallel and serial output drivers.

- The ADS7806 can acquire and convert to full 12-bit accuracy in **25µs** max, while consuming only 35mW max. **Laser trimmed scaling resistors** provide standard industrial input ranges of ±**10V** and **0V to +5V**. In addition, a 0V to +4V range allows development of complete single-supply systems.

The ADS7806 is available in a 0.3" DIP-28 and SO-28, both fully specified for operation over the industrial -40°C to +85°C temperature range.

Measurement Technologies

|     |          | 200              |          |                                                                                                                                                                                                                    |

|-----|----------|------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | PIN D    | ESCRIPT          | TIONS    |                                                                                                                                                                                                                    |

|     |          |                  | DIGITAL  |                                                                                                                                                                                                                    |

|     | PIN#     | NAME             | I/O      | DESCRIPTION                                                                                                                                                                                                        |

|     | 1        | R1 <sub>IN</sub> |          | Analog Input. See Figure 7.                                                                                                                                                                                        |

|     | 2        | AGND1            |          | Analog Sense Ground                                                                                                                                                                                                |

|     | 3        | R2 <sub>IN</sub> |          | Analog Input See Figure 7.                                                                                                                                                                                         |

|     | 4        | CAP              |          | Reference Buffer Output. 2.2μF tantalum capacitor to ground.                                                                                                                                                       |

|     | 5        | REF              |          | Reference Input/Output. 2.2μF tantalum capactor to ground.                                                                                                                                                         |

|     | 6        | AGND2            |          | Analog Ground                                                                                                                                                                                                      |

|     | 7        | SB/BTC           |          | Selects Straight Binary or Binary Two's Complement for Output Data Format.                                                                                                                                         |

|     | 8        | EXTINT           | l i      | External/Internal data clock select.                                                                                                                                                                               |

|     | 9        | D7               | 0        | Data Bit 3 if BYTE is HIGH. Data bit 11 (MSB) if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW. Leave                                                                                                        |

|     | 40       | D6               | 0        | unconnected when using serial output.  Data Bit 2 if BYTE is HIGH. Data bit 10 if BYTE is LOW. Hi-Z when CS is HIGH and/cr R/C is LOW.                                                                             |

|     | 10<br>11 | D6               | 0        | Data Bit 1 if BYTE is HIGH. Data bit 10 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.                                                                                                                    |

|     | 11       | D4               | 0        | Data bit 1 if by IE is High. Data bit 9 if by IE is LOW. Hi-Z when CS is High and/or R/C is LOW.  Data Bit 0 (LSB) if ByTE is High. Data bit 9 if ByTE is LOW. Hi-Z when CS is High and/or R/C is LOW.             |

|     | 13       | D3               | 0        | LOW f BYTE is HIGH. Data bit 7 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.                                                                                                                             |

|     | 14       | DGND             | 0        | Digital Ground                                                                                                                                                                                                     |

|     | 15       | D2               | 0        | LOW if BYTE is HIGH, Data bit 6 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.                                                                                                                            |

|     | 16       | D1               | ŏ        | LOW if BYTE is HIGH. Data bit 5 if BYTE is LOW. Hi-Z when CS is HIGH and/or R/C is LOW.                                                                                                                            |

|     | 17       | D0               | ő        | LOW f BYTE is HICH. Data bit 4 if BYTE is LOW. Hi-Z when CS is HICH and/or R/C is LOW.                                                                                                                             |

|     | 18       | DATACLK          | VO.      | Data Clock Output when EXT/INT is LOW. Data clock input when EXT/INT is HIGH.                                                                                                                                      |

|     | 19       | SDATA            | 0        | Serial Output Synchronized to DATACLK                                                                                                                                                                              |

|     | 20       | TAG              | ĭ        | Serial Input When Using an External Data Clock                                                                                                                                                                     |

|     | 21       | BYTE             | i        | Selects 8 most significant bits (LOW) or 4 least significant bits (HIGH) on parallel output pins.                                                                                                                  |

|     | 22       | R∕C              | 1        | With CS LOW and 3USY HIGH, a Falling Edge on R/C Initiates a New Conversion. With CS LOW, a rising edge on R/C enables the parallel output.                                                                        |

|     | 23       | CS               | ı        | Internally OR'ed with RIC. If RIC is LOW, a falling edge on CS initiates a new conversion. If EXT/INT is LOW, this same                                                                                            |

|     | 24       | BUSY             | 0        | falling edge will start the transmission of serial data results from the previous conversion.  At the start of a conversion, BUSY goes LOW and stays LOW until the conversion is completed and the digital outputs |

|     |          |                  | ١.       | have been updated                                                                                                                                                                                                  |

|     | 25       | PWRD             | !        | PWRD HIGH shuts down all analog circuitry except the reference. Digital circuitry remains active.                                                                                                                  |

|     | 26       | REFD             |          | REFD HIGH shuts down the internal reference. External reference will be required for conversions.                                                                                                                  |

|     | 27<br>28 | VANA             |          | Analog Supply, Nominally +5V. Decouple with 0.1µF ceramic and 10µF tantalum capacitors.                                                                                                                            |

|     | 20       | V <sub>DIG</sub> |          | Digital Supply. Nominally –5V. Connect directly to pir 27. Must be ≤ V <sub>ANA</sub> .                                                                                                                            |

| Hay | _        | Measure          | ment Lec | nnologies                                                                                                                                                                                                          |

|                                                                                     |                                  | ADS7806P, U |               |          | ADS7806PB, UB |           |       |        |

|-------------------------------------------------------------------------------------|----------------------------------|-------------|---------------|----------|---------------|-----------|-------|--------|

| PARAMETER                                                                           | CONDITIONS                       | MIN         | TYP           | MAX      | MIN           | TYP       | MAX   | UNIT   |

| RESOLUTION                                                                          |                                  |             |               | 12       |               |           | *     | Ві     |

| ANALOG INPUT<br>Voltage Ranges                                                      |                                  |             |               |          | +5, 0 to +4   |           |       | ١      |

| Impedance<br>Capacitance                                                            |                                  |             | 35            | (See 1   | Table I)      | *         |       | р      |

| THROUGHPUT SPEED                                                                    |                                  |             |               |          |               |           |       |        |

| Conversion Time<br>Complete Cycle                                                   | Acquire and Convert              |             |               | 20<br>25 |               |           | *     | μ<br>u |

| Throughput Rate                                                                     | Acquire and Convert              | 40          |               | 23       | *             |           | *     | ki     |

| DC ACCURACY                                                                         |                                  |             |               |          |               |           |       |        |

| Integral Linearity Error                                                            |                                  |             | ±0.15         | ±0.9     |               | *         | ±0.45 | LS     |

| Differential Linearity Error                                                        |                                  |             | ±0.15         | ±0.9     |               | *         | ±0.45 | L      |

| No Missing Codes<br>Transition Noise <sup>(2)</sup>                                 |                                  |             | Tested<br>0.1 |          |               | *         |       | В      |

| Gain Error                                                                          |                                  |             | ±0.2          |          |               | *<br>±0.1 |       | L      |

| Full-Scale Error <sup>(3,4)</sup>                                                   |                                  |             | ±0.2          | ±0.5     |               | ±0.1      | ±0.25 |        |

| Full-Scale Error Drift                                                              |                                  |             | +7            | 10.5     |               | ±5        | 10.25 | ppr    |

| Full-Scale Error(3,4)                                                               | Ext. 2.5000V Ref                 |             | 11            | ±0.5     |               | 10        | ±0.25 | ppi    |

| Full-Scale Error Drift                                                              | Ext. 2.5000V Ref                 |             | ±0.5          | 10.0     |               | *         | 10.20 | ppr    |

| Bipolar Zero Error <sup>(3)</sup>                                                   | ±10V Range                       |             | 10.0          | ±10      |               | **        | *     | l bb   |

| Bipolar Zero Error Drift                                                            | ±10V Range                       |             | ±0.5          | -10      |               | *         |       | ppr    |

| Unipolar Zero Error <sup>(3)</sup>                                                  | 0V to 5V, 0V to 4V Ranges        |             |               | ±3       |               |           | *     | l PP   |

| Unipolar Zero Error Drift                                                           | 0V to 5V, 0V to 4V Ranges        |             | ±0.5          |          |               | *         |       | ppr    |

| Recovery Time to Rated Accuracy<br>from Power-Down <sup>(5)</sup>                   | 2.2µF Capacitor to CAP           |             | 1             |          |               | *         |       | n      |

| Power-Supply Sensitivity<br>(V <sub>DIG</sub> = V <sub>ANA</sub> = V <sub>S</sub> ) | +4.75V < V <sub>S</sub> < +5.25V |             |               | ±0.5     |               |           | *     | L      |

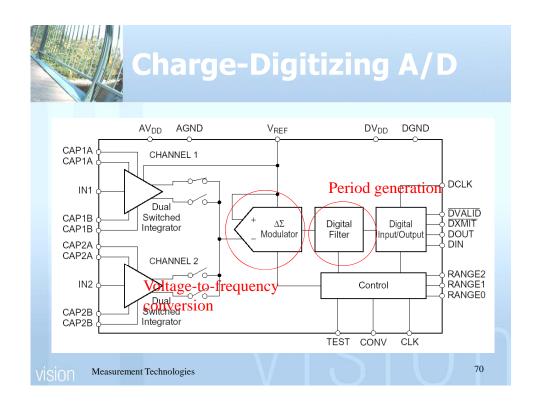

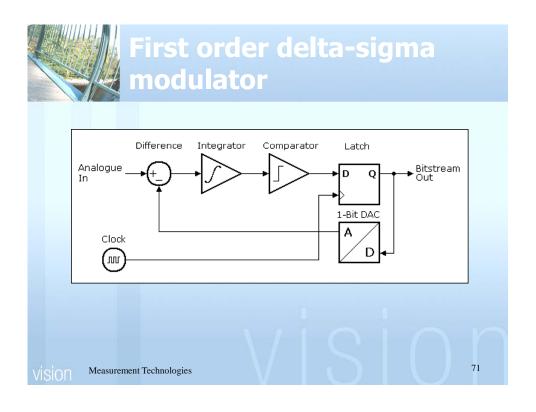

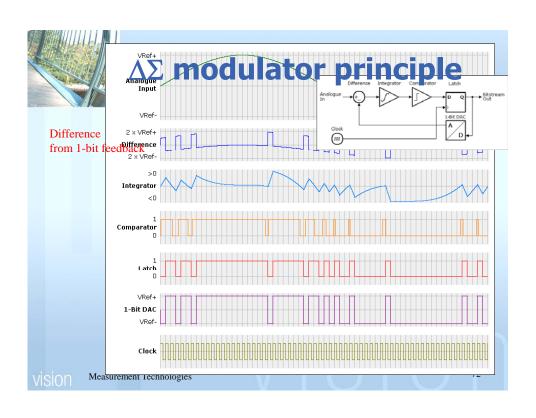

# $\Delta\Sigma$ Converter

- Converting amplitude into frequency

- Utilizing the fast clock rate in modern IC

- Achieving fast conversion with high resolution

- Scalable compromise between resolution and speed

- Low operating voltage

- Example TI ADS7806

Measurement Technologies

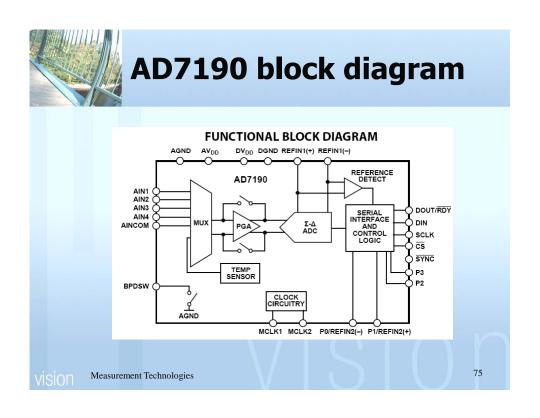

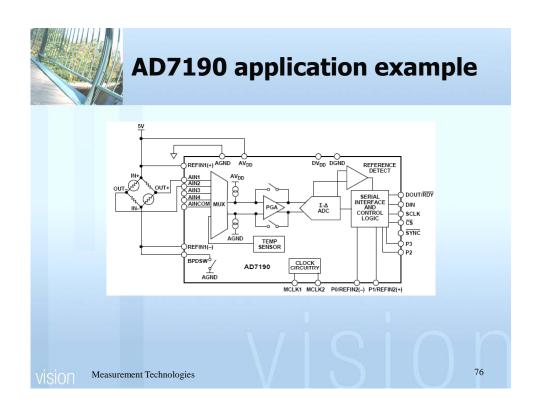

## **Analog Device AD7190**

- GENERAL DESCRIPTION

- Low noise, complete analog front end for high precision measurement applications. It contains a low noise, 24-bit sigma-delta (Σ-Δ) analog to digital converter (ADC). On-Chip low noise gain stage allow signals of small amplitude can be interfaced directly to the ADC.

- Two differential inputs or four pseudo differential inputs. The on-chip channel sequencer allows several channels to be enabled, and the AD7190 sequentially converts on each enabled channel. This simplifies communication with the part. The on-chip 4.92 MHz clock can be used as the clock source to the ADC or, alternatively, an external clock or crystal can be used. The output data rate from the part can be varied from 4.7 Hz to 4.8 kHz.

- Two digital filter options. The choice of filter affects the rms noise/noise-free resolution at the programmed output data rate, the settling time, and the 50 Hz/60 Hz rejection. For applications that require all conversions to be settled, the AD7190 includes a zero latency feature.

- Operates with 5 V analog power supply and a digital power supply from 2.7 V to 5.25 V. It consumes a current of 6 mA. It is housed in a

Measurement T24 ilendie SSOP package.

73

# **Analog Device AD7190**

#### FEATURES

- RMS noise: 8.5 nV @ 4.7 Hz (gain = 128)

- **16 noise free bits** @ 2.4 kHz (gain = 128)

- Up to 22.5 noise free bits (gain = 1)

- Offset drift: 5 nV/°C

- Gain drift: 1 ppm/°C

- Specified drift over time

- 2 differential/4 pseudo differential input channels

- Automatic channel sequencer

- Programmable gain (1 to 128)

- Output data rate: 4.7 Hz to 4.8 kHz

- Internal or external clock

- Simultaneous 50 Hz/60 Hz rejection

- 4 general-purpose digital

- Power supply

- AVDD: 4.75 V to 5.25 V

- DVDD: 2.7 V to 5.25 V

- Current: 6 mA

- Temperature range: -40°C to +105°C

- Interface

- 3-wire serial

- SPI, QSPI<sup>™</sup>, MICROWIRE<sup>™</sup>, and DSP compatible

- Schmitt trigger on SCLK

#### APPLICATIONS

- Weigh scales

- Strain gauge transducers

- Pressure measurement

- Temperature measurement

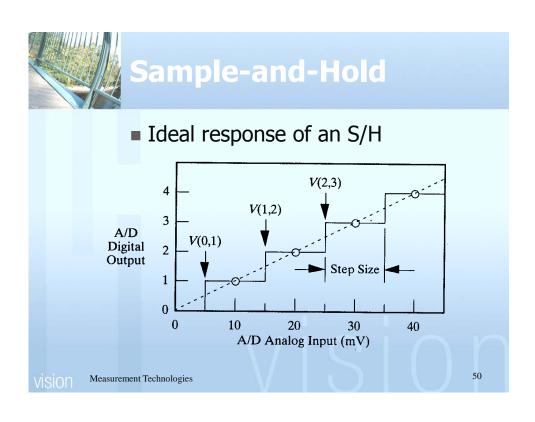

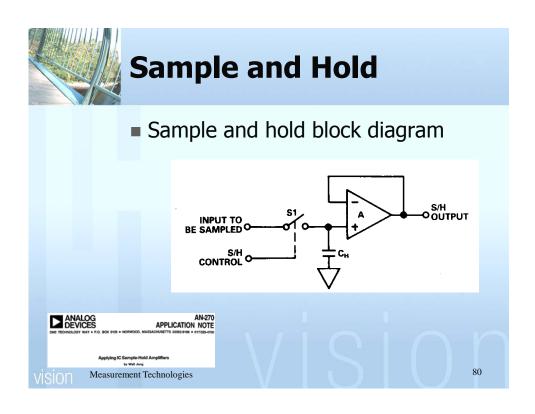

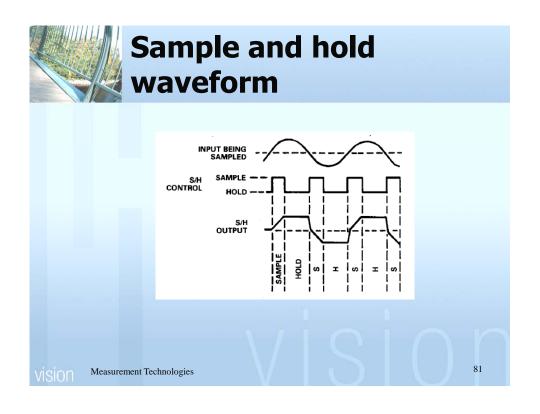

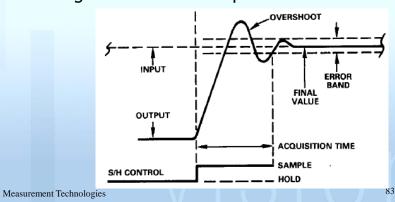

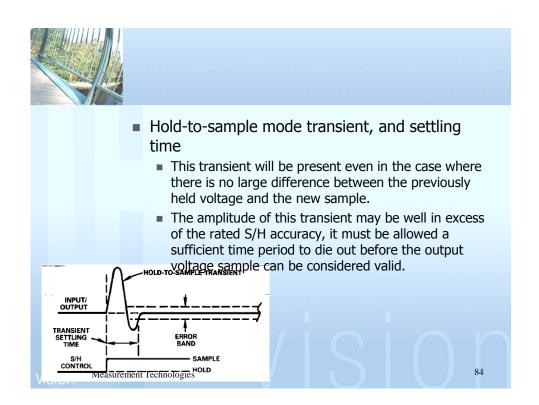

# **Hold-to-sample transition errors**

Acquisition time – time required for the S/H to acquire and than track the input signal after the "sample" commend.

# **Dielectric Absorption**

With some common capacitor types, the dielectric does not completely release all of its energy after a charge/discharge cycle.

visior

Measurement Technologies

93

# **Drift and Noise**

- A S/H can possess different drift characteristics in the HOLD mode than those in the SAMPLE mode.

- In the HOLD mode, the output terminal sees only the drift of the output buffer amplifier.

- In the SAMPLE mode, it sees either the input amplifier alone or the composite drift of two series amplifiers.

VISIO

Measurement Technologies